# Software and Hardware Engineering Assembly and C Programming for the Freescale HCS12 Microcontroller

Instructor's Solution Manual

### **Contents**

| CHAPTER 2 GENERAL PRINCIPLES OF MICROCONTROLLERS            | 1   |

|-------------------------------------------------------------|-----|

| CHAPTER 3 STRUCTURED PROGRAM DESIGN                         | 4   |

| CHAPTER 4 INTRODUCTION TO THE HCS12 HARDWARE                | 11  |

| CHAPTER 5 AN ASSEMBLER PROGRAM                              | 14  |

| CHAPTER 6 THE LINKER                                        | 17  |

| CHAPTER 7 THE HCS12 INSTRUCTION SET                         | 21  |

| CHAPTER 8 ASSEMBLY LANGUAGE PROGRAMS FOR THE HCS12          | 33  |

| CHAPTER 10 PROGRAM DEVELOPMENT USING C                      |     |

| CHAPTER 11 HCS12 PARALLEL I/O                               |     |

| CHAPTER 13 HCS12 MEMORIES                                   | 81  |

| CHAPTER 14 HCS12 TIMER                                      | 82  |

| CHAPTER 15 HCS12 SERIAL I/O – SCI AND SPI                   | 105 |

| CHAPTER 16 HCS12 SERIAL I/O - MSCAN                         | 118 |

| CHAPTER 17 HCS12 ANALOG INPUT                               |     |

| CHAPTER 18 SINGLE CHIP MICROCOMPUTER INTERFACING TECHNIQUES |     |

| Chapter 19 HCS12 FUZZY LOGIC                                |     |

| APPENDIX A BINARY CODES                                     | 130 |

| SETTING UP FILES IN CODEWARRIOR FOR THE LAB                 | 137 |

## Chapter Problems and Solutions

A letter or letters in [...] at the end of each of the end of chapter problems signifies that the problem in some way tests that the student meets ABET accreditation criteria for Outcomes a - k as follows:

- a. An ability to apply knowledge of mathematics, science, and engineering.

- b. An ability to design and conduct experiments, as well as to analyze and interpret data.

- c. An ability to design a system, component, or process to meet desired needs.

- d. An ability to function on multi-disciplinary teams.

- e. An ability to identify, formulate, and solve engineering problems.

- f. An understanding of professional and ethical responsibility.

- g. An ability to communicate effectively.

- h. The broad education necessary to understand the impact of engineering solutions in a global and societal context.

- i. A recognition of the need for, and an ability to engage in lifelong learning.

- j. A knowledge of contemporary issues.

- k. An ability to use the techniques, skills and modern engineering tools necessary for engineering practice.

#### CHAPTER 2 GENERAL PRINCIPLES OF MICROCONTROLLERS

#### Basic:

**2.1** What is the difference between an assembler and a compiler? [a, c]

An assembler converts an assembly language program consisting of operations and their operands into the machine language (1s and 0s) for the microcontroller.

A compiler converts a high-level language, such as C, first into the assembly language needed for the line of C code, and then into the machine language for the microcontroller.

2.2 What is the advantage of a relocatable assembler compared to an absolute assembler? [a]

A relocatable assembler allows a program to be written in separate modules that are linked together to form the program. This permits modular design. An absolute assembler must have all its modules in one big program. This limits our ability to use pre-written and tested modules from a library of useful functions.

**2.3** What is a microcontroller memory map? [a]

This shows what kind of memory is located in what address space.

**2.4** What does a sequence controller do? [a]

Generates the sequence of control signals needed to execute an instruction.

- **2.5** Give short answers to the following: [a,g]

- a. What is a data bus?

A parallel, bidirectional, binary information pathway with multiple sources and destinations.

b. Why is an address decoder used in I/O interfaces?

To select one-of-many sources or destinations.

c. How is an information source, such as a set of switches interfaced to a data bus?

With three-state gates whose enable is controlled by an Address\_OK signal and a Read control signal.

d. What control signals are needed to latch data from the data bus into an output interface at the correct time?

Address\_OK and Write

e. Give the sequence of events that occur when a CPU does an input (or read) cycle.

CPU puts address on the address bus Address decoder generates ADR\_OK CPU asserts READ control signal Input device puts data on the data bus CPU reads the data CPU de-asserts READ control signal

#### **Intermediate:**

**2.6** Discuss the difference between an absolute and a relocatable assembler. [a, k]

Absolute Assembler: You must locate the code at assembly time and all code must be in one file. All defined labels are globally known.

Relocatable Assembler: A linker is used to locate the final code; modular software development with files separately developed and assembled may be used.

2.7 How do most microcomputer systems solve the problem of multiple sources of information present on a data bus? [g]

Multiple sources can exist as long as addressing and address decoding is used to enable one and only one source through three-state gates at any one time.

#### Advanced:

**2.8** Why must a tristate gate be used to interface an input device to the data bus? [a, c]

The tristate gate allows multiple sources to source their data, one at a time, onto the data bus. The CPU's read control signal and an address decoder must control the tristate gate's enable.

2.9 Why must a latch be used to interface an output device to the data bus? [a, c]

The data bus is active all the time with data flowing to and from memory and I/O devices. To be able to output specific data to an output device at a specific time, a latch must be used which is clocked by the write control signal and the correct address.

2.10 For a CPU performing a write cycle, why does the CPU place the data on the data bus before asserting the WR\_L control signal? [a]

To satisfy the data setup time requirement of the latch.

- 2.11 A microcontroller memory map shows 16K bytes of Flash EEPROM (ROM) in memory space \$C000 \$FFFF and 1 Kbyte of RAM in memory space \$1000 \$13FF. [c, k]

- a. Give a range of addresses (in hex) suitable for locating code:

\$C000 - \$FFFF

b. Give a range of addresses (in hex) suitable for allocating variable data storage:

\$1000 - \$13FF

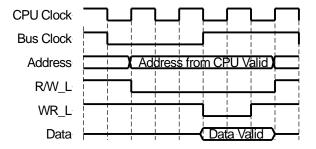

Draw a timing diagram relative to the CPU clock shown in the figure below, which includes the address and data buses, R/W\_L and the write control signal (WR\_L = active low) and which shows a write cycle.

[a]

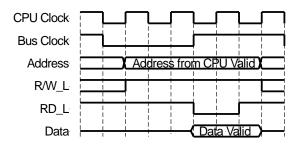

2.13 Draw a timing diagram relative to the system CPU clock shown in the figure below, which includes the address and data buses, R/W\_L, and the read control signal (RD\_L = active low) and which shows a read cycle. [a]

#### CHAPTER 3 STRUCTURED PROGRAM DESIGN

#### **Basic:**

**3.1.** List at least five principles of top-down design. [a, c]

Understand the problem completely; design in levels; ensure correctness at each level; postpone details; successively refine your design; design without using a programming language.

**3.2.** What are the three basic elements of structured programming? [a]

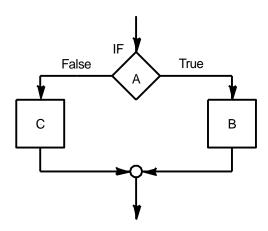

SEQUENCE; IF-THEN-ELSE; REPETITION

**3.3.** Write the pseudocode and draw the flow chart symbol to represent the decision IF A is TRUE THEN B ELSE C. [a, c]

```

IF A

THEN

Begin B

End B

ELSE

Begin C

End C

ENDIF A

```

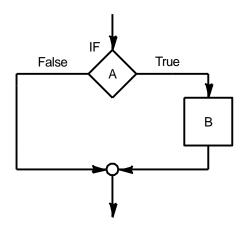

**3.4.** Write the pseudocode and draw the flow chart symbol to represent the decision IF A is TRUE THEN B. [a, c]

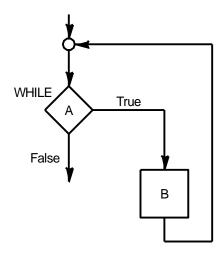

**3.5.** Write the pseudocode and draw the flow chart symbol to represent the repetition WHILE A is TRUE DO B. [a, c]

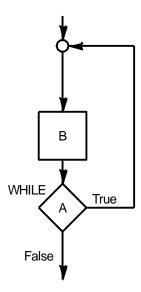

**3.6.** Write the pseudocode and draw the flow chart symbol to represent the repetition DO B WHILE A is TRUE. [a, c]

DO

Begin B

...

End B

ENDO B

WHILE A

ENDO WHILE A

#### **Intermediate:**

**3.7.** Write a design using structured flow charts or pseudocode to implement the following problem description: [c]

Prompt for and input a character from a user at the keyboard.

If the character is alphabetic and is uppercase, change it to lowercase and output it to the screen.

If the character is alphabetic and is lowercase, change it to uppercase and output it to the screen.

If the character is numeric, output it with no change.

If it is any other character, beep the bell.

Repeat this process until an ESC character is typed by the user.

```

Output a prompt

Input a character

IF the character is alphabetic

IF the character is uppercase

THEN

Change the character to lowercase

ELSE

Change the character to uppercase

ENDIF the character is uppercase

Output the character to the screen

ELSE

IF the character is numeric

THEN

Output the character to the screen

ELSE

Output a bell to the screen

ENDIF it is numeric

ENDIF the character is alphabetic

WHILE The character is not an ESC

```

#### Advanced:

3.8. Design a program that initializes an 8-bit data storage accumulator to 0 and then inputs 10<sub>10</sub> successive 8-bit values from an input device located at address \$70, adding each of them to the 8-bit data storage accumulator. If during this process an unsigned binary overflow occurs, print an error message and repeat from the beginning. Otherwise, after the 10 values have been input and added, output the result to an output device at location \$71. Run the process forever. Your design must be a structured design and must show sequence, decision and repetition. [c]

```

DO

Initialize accumulator to zero

Initialize a counter to 10

WHILE there is no unsigned overflow and counter > 0

DO

Get a value from $70

Add it to the accumulator

Save overflow indication

Decrement counter

ENDDO

ENDWHILE there is no unsigned overflow and counter >0

IF overflow occurred

THEN

Print the overflow error message

Output the accumulator to $71

ENDIF overflow occurred

ENDDO

FOREVER or WHILE (1)

```

**3.9.** Give a design using structured pseudocode to accomplish the following: [c]

A user is to input a character to select one of three processes. Valid characters are A, B, and C. A, B, and C select processes A, B, or C, respectively. Process A requires a byte of information to be input from an A/D converter, which it then converts to an integer decimal number in the range of 0 to 5 and displayed on the screen. Process B and C are not defined at this stage. Prompts and error messages are to be displayed. You do not have to give details of the decimal conversion required in Process A.

```

Prompt user for character A, B, or C

Get the character

IF the character is A

THEN

Get input from the A/D

Convert it to an integer decimal number in the range of 0 to 5

Display the value on the screen

ELSE

IF the character is B

THEN

Do process B

ELSE

IF the character is C

THEN

DO process C

ELSE

Print error message that user did not enter A, B, or C

ENDIF the character is C

ENDIF the character is B

ENDIF the character is A

```

#### **3.10.** Give a design using structured pseudocode to accomplish the following: [c]

A byte of data is to be input from an analog-to-digital converter and a critical value is to be input from a set of switches. If the A/D value is greater than the critical value, the microcontroller is to sound an alarm. Otherwise the alarm is to be turned off. This process is to continue forever.

```

Input data from A/D

Input data from switches

IF A/D value is greater than the switches value

THEN

Turn the alarm on

ELSE

Turn the alarm off

ENDIF A/D value is greater than the switches

ENDDO

FOREVER or WHILE(1)

```

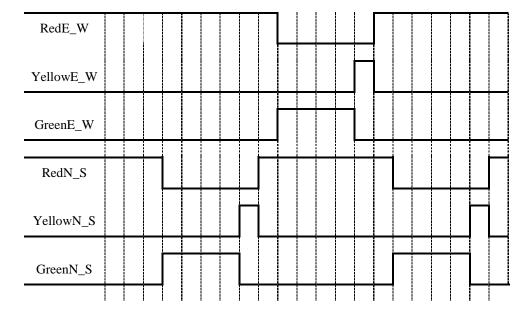

#### **3.11.** Design a traffic light controller: [c]

Imagine an intersection with North/South and East/West streets. There are to be six traffic light signals:

```

RedE_W, YellowE_W, GreenE_W

RedN_S, YellowN_S, GreenN_S

```

Assume the time elements in the table shown are 10 seconds and that a timer delay is available as a function or subroutine. Give the pseudocode structured design for the light controller.

```

Start with GreenN_S coming on:

Initial conditions: Turn RedE_W on and RedN_S on. All others off.

DO

Turn RedN_S off and GreenN_S and RedE_W on.

Wait 40 seconds

Turn YellowN_S and RedE_W on and GreenN_S off

Wait 10 seconds

Turn RedN_S and RedE_W on and YellowN_S off.

Wait 10 seconds

Turn RedE_W off and GreenE_W and RedN_S on

Wait 40 seconds

Turn YellowE_W and RedN_S on and GreenE_W off

Wait 10 seconds

Turn RedE_W and RedN_S on and YellowE_W off

Wait 10 seconds

Turn RedE_W and RedN_S on and YellowE_W off

Wait 10 seconds

FOREVER

```

#### CHAPTER 4 INTRODUCTION TO THE HCS12 HARDWARE

#### **Basic:**

**4.1.** Which of the HCS12 ports is used for the A/D converter inputs? [a]

**PORTAD**

**4.2.** Which of the HCS12 ports is used with serial I/O? [a]

PTS for the SCI, PTM for the SPI

**4.3.** Draw the programmer's model for the HCS12. [a]

| 7  | ACCUMULATOR A 0            | 7 ACCUMULATOR B 0 |  |

|----|----------------------------|-------------------|--|

| 15 | DOUBLE ACCUMULATOR D 0     |                   |  |

| 15 | INDEX REGISTER X 0         |                   |  |

| 15 | INDEX REGISTER Y 0         |                   |  |

| 15 | STACK POINTER 0            |                   |  |

| 15 | PROGRAM COUNTER 0          |                   |  |

|    | CONDITION CODE<br>REGISTER | SXHINZVC          |  |

- **4.4.** Which bits in the HCS12 condition code register may be tested with conditional branching instructions? [a] *NZVC*

- **4.5.** Complete the following sentences to describe the operation of the bits in the condition code register: [a]

- a. The N bit is set when the most significant bit of the result is 1.

- b. The Z bit is set when all bits of the result are 0.

- c. The V bit is set when *two's complement overflow occurs*.

- d. The C bit is set when *carry out or borrow out occurs*.

- **4.6.** Describe the following HCS12 addressing modes: [g]

immediate, direct, extended, indexed, indexed-indirect, inherent, relative.

Immediate: The data for the instruction immediately follows the op code. Immediate addressing is used for constants known at the time the program is assembled.

Direct: Direct addressing uses an 8-bit address to directly access a location in the first 256 bytes of memory.

Extended: Extended addressing uses a 16-bit address to access a memory location anywhere in the 64 Kbyte address space.

Indexed: Indexed addressing generates the effective address by adding a 5-, 9- or 16-bit signed constant offset (specified by the instruction) to the contents of the IX, IY, SP or PC registers. A 16-bit address is the result.

Indexed-Indirect: This mode uses indexed addressing to find the address of the memory location that contains the address of the data.

Inherent: Inherent addressing means the instruction itself specifies where the operand is located.

Relative: Relative addressing is used for branch instructions. An 8-bit, two's complement offset specified by the instruction is added to the contents of the program counter.

#### **Intermediate:**

- **4.7.** Calculate the effective address for each of the following examples of indexed addressing. [a]

- a. X = \$0800

ldaa 0,

$$X = EA = $0800$$

b. Y = \$0800

staa \$10, Y

$$EA = $0810$$

c. X = \$080D

ldaa \$25,

$$\times EA = \$0832$$

**4.8.** Discuss the relative advantages and disadvantages of direct and extended addressing. [g]

Direct addressing uses only eight bits to specify the address of the memory data and thus is faster and uses less memory than extended addressing. Its disadvantage is that only 256 memory locations can be addressed.

Extended addressing requires three (or more) bytes for the instruction and address and thus takes longer to execute and requires more memory. Extended addressing can access the whole 64 Kbyte address space.

**4.9.** Discuss the relative advantages and disadvantages of extended and indexed addressing. [g]

Indexed addressing is a two byte instruction (for the X register, three bytes for the Y register). Thus it is faster and uses less memory than extended addressing. Its major advantage is that the address of the data can be determined at run-time and the index register can be incremented and decremented to step through tables of data.

- **4.10.** What is in the following CPU registers after a system reset? [a]

- A, B, CCR, Stack Pointer.

Except for the I, S, and X bits in the CCR, the state of these registers after a system reset is undetermined.

#### Advanced:

- **4.11.** What HCS12 addressing mode is best to use when you want to access a number of sequential elements in a data array? [a]

- a. Immediate

- b. Direct

- c. Extended

- d. Indexed

- e. None of these

d. Indexed

- **4.12.** What HCS12 addressing mode is best to use when you want to compare what is in accumulator A with a constant? [a]

- a. Immediate

- b. Direct

- c. Extended

- d. Indexed

- e. None of these

- a. Immediate